Novità dell'architettura Sandy Bridge - 2

TURBO BOOST DI SECONDA GENERAZIONE

L’idea di sfruttare dinamicamente il TDP a disposizione per incrementare la frequenza di clock di uno o più core è sta introdotta con l’architettura Nehalem ed ha avuto la sua massima espressione nelle CPU Lynnfield. La chiave di volta del Turbo Boost è sicuramente la capacità di queste CPU di essere stabili a frequenze di lavoro superiori a quelle nominali anche con vcore default. Grazie a questa peculiarità la CPU effettua una sorta di overclock dinamico aumentando il moltiplicatore di uno o più core in base al carico applicativo, fino a raggiungere la soglia massima di consumo determinata dal TDP.

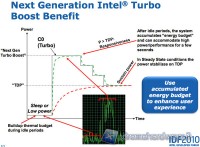

Il Turbo Boost introdotto nelle CPU Sandy Bridge presenta delle importanti novità che lo rendono ancora più dinamico e reattivo. Sfruttando il fatto che, al momento di entrata in funzione del turbo, la CPU non raggiunge il TDP istantaneamente ma con una curva con un coefficiente di salita a volte anche piuttosto lento, ovvero di diversi minuti, Intel ha pensato di aumentare il moltiplicatore del turbo boost nei primi istanti di attivazione, per poi calare progressivamente fino al raggiungimento dell’asintoto del TDP. L’effetto di questo boost aggiuntivo nei primi istanti è tanto più benefico quando la richiesta di potenza di calcolo è discontinua, permettendo di massimizzare le performance quando ce n’è necessità.

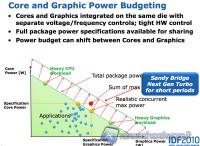

Un altro miglioramento è stato introdotto aggiungendo più step intermedi al turbo boost e aumentando la flessibilità del sistema di gestione, che tra le altre cose deve tenere in conto anche della presenza della GPU integrata nel chip, dovendo rientrare anch’essa nel limite del TDP.

In caso di utilizzo della grafica integrata, quindi, il Turbo Boost bilancerà adeguatamente e dinamicamente le frequenze e i consumi tra le due parti che compongono Sandy Bridge: la CPU e la GPU. Ovviamente il trade-off sarà valutato in base al tipo di applicativo, favorendo la CPU in caso di necessità di calcoli computazionali, o favorendo la GPU in caso di grafica 3D.

RING BUS E SYSTEM-AGENT

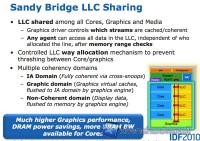

Come rendere una piattaforma scalabile a più core senza dover aumentare a dismisura l’area necessaria per realizzarla e con costi di produzione contenuti? Il problema principale che si presenta nelle CPU multi-core è l’accesso ad una cache condivisa. In Sandy Bridge oltre ai due o quattro core presenti, devono accedere alla cache L3 anche la GPU e il System Agent, che integra le funzioni del vecchio NorthBridge, ormai integrato totalmente nella CPU.

La soluzione è l’utilizzo di un bus ad anello che interconnette la cache condivisa alle varie unità che devono accedervi. Questa soluzione non è una novità assoluta poiché è stata già adottata nelle CPU Nehalem EX e Westmere EX per piattaforme server multi-processore. L’idea di sfruttare un bus ad anello deriva dal fatto che collegare tutti i componenti della CPU direttamente alla cache comporta l’utilizzo di connessioni punto-punto che creano grossi problemi di wiring, oltre che aumentano a dismisura l’area occupata nel die. Il ring bus viene invece sovrapposto direttamente alla cache, in un layer apposito di metallizzazione dedicato. Il bus è in realtà composto da 4 anelli indipendenti dedicati rispettivamente a:

- Data

- Request

- Acknowledgement

- Snoop

Il bus è in grado di accettare 32Byte di dati ad ogni ciclo di clock ad ogni nodo dell’anello, ottenendo una Bandwidth di accesso alla cache per ogni core di circa 96GB/s e una bandwidth aggregata per un quad-core di 384GB/s. Un altro beneficio del ring bus è la latenza di accesso alla cache L3 estremamente ridotta, rispetto anche alle precedenti architetture Nehalem.

Il ring bus utilizza sofisticati algoritmi di arbitraggio che permettono di minimizzare le latenze. L’architettura è inoltre facilmente scalabile a piattaforme multiprocessore. Dobbiamo quindi aspettarci l’utilizzo anche per le future CPU a 8 core destinate alle future piattaforme LGA 2011.

SYSTEM AGENT

Intel ha abbandonato il concetto di uncore (tutto ciò che non è core), che in Nehalem comprendeva anche la cache L3, in favore del System Agent, praticamente un NorthBridge integrato nella CPU. Il System Agent si occupa della gestione del Memory Controller, con latenze ridotte rispetto al memory controller delle CPU Clarkdale e comparabili rispetto a quelle delle CPU Lynnfield, della gestione delle 16 linee PCI-Express 2.0, generalmente separate in 2 linee x8, del controller dell’uscita a video, integrato nella CPU per risparmiare potenza nelle piattaforme notebook, e, non ultimo, dell bus DMI che interconnette la CPU con il chipset (o Platform Controller Hub) H67 o P67. Interessante notare come System Agent, Core e GPU hanno differenti alimentazioni e anche frequenze di clock, per una gestione del tutto indipendente.

Ovviamente anche in questo caso, come è accaduto in passato con l’uncore, il System Agent avrà frequenze di clock inferiori rispetto a quelle del core.